Xilinx官方授权FPGA培训系列课程 -- 多核异构MPSoC软硬件开发及其AI应用

Xilinx SoC 产品系列将处理器的软件可编程性与 FPGA 的硬件可编程性进行完美整合,可为您提供无与伦比的系统性能、灵活性与可扩展性。该产品系列可为您的设计带来更低功耗与更低成本的整体系统优势以及快速上市进程。与传统 SoC 处理解决方案不同,高度灵活的可编程逻辑可为您实现优化和差异化,允许您添加外设与加速器,从而可帮助您适应各种广泛的应用。作为SoC产品中的高端系列Zynq® UltraScale+™ MPSoC 器件,不仅提供 64 位处理器可扩展性,同时还将实时控制与软硬件引擎相结合,支持图形、视频、波形与数据包处理。置于包含通用实时处理器和可编程逻辑的平台上, 为 5G 无线、视频图像处理、下一代 ADAS 和工业物联网等领域创造了无限可能性。

为了能让工程师尽快掌握异构多核MPSoC的特性和优势以设计更智能更灵活的系统,提高产品竞争力和加速产品上市进程,依元素科技推出为期3天的专题培训班。 本培训课程主要介绍Zynq UltraScale+ MPSoC架构及其内部模块,旨在为您设计异构多核MPSoC项目提供决策,主要包括APU、RPU、PMU等模块,也将介绍PS和PL如何有效互联,如何正确进行启动和配置、如何保护系统及一致性要求等。同时,本课程最后还将基于MPSoC平台,运用Xilinx最新的Vitis AI开发套件,通过不同的实际案例,一步一步地教会您实现边缘端的深度学习推断加速。

一、培训对象

1.使用过EDK工具并且打算转换为最新的Vivado工具来开发项目的工程师

2.致力于借助MPSoC 加快系统开发进程的软/硬件工程师

3.希望基于MPSoC实现“硬件加速”以提升系统性能的软/硬件工程师

4.希望进行人工智能开发的软/硬件工程师

二、培训目标

1.了解异构多核MPSoC系统的基本架构;

2.了解APU架构及其输入输出外设;

3.了解RPU架构及其特性;

4.了解PS/PL互联AXI接口并学会构建一个基本的完整系统;

5.了解MPSoC启动和配置过程;

6.了解PMU单元并有效进行电源管理;

7.了解时钟和复位功能;

8.学会基本的嵌入式Linux开发流程;

9.了解Vitis AI开发环境并做好搭建;

10.了解DPU单元并能做一些基本应用开发。

三、学员基础

1.具有一定的HDL语言基础

2.具有一定的数字设计经验

3.基本了解微处理器架构

4.基本了解C编程

5.了解基本的机器学习概念(可选)

四、教学平台

Xilinx Zynq UltraScale+ MPSoC开发平台ZCU104,供现场实际动手操作。

五、软件工具

1.Vivado System Edition 2019.2;

2.Vitis AI Development Kit v1.1(适用于AI内容);

3.Ubuntu 18.04 64位OS(适用于AI内容);

4.Docker (适用于AI内容);

六、师资团队

讲师团队来自于通过Xilinx官方认证的培训讲师及行业精英组成,具有丰富的FPGA系统项目的开发经验。领先的FPGA理论和丰富的实战经验,将带给学员以从不同的视角来掌握FPGA系统开发的精髓,部分师资介绍:

Robert Zhou:知名高校硕士学位,具有10年以上FPGA项目开发和技术支持经验,并具有多年的FPGA企业培训经验。

马仁安,博士,长期从事影像处理、机器视觉和人工智能等方向的应用研究与开发,Xilinx首批通过Vitis认证考核讲师。

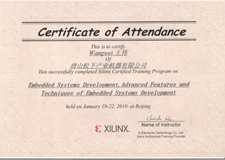

七、证 书

培训结束,理论、实践双项考核成绩合格者,颁发Xilinx官方授权培训FPGA工程师证书。

八、培训时间、地点及费用

1.时间:2020年8月29日-31日

2.地点:依元素科技南京培训基地(南京市江北新区星火路15号智芯科技楼十楼1012室)

3.课程费用:

人民币3280元/人(不含AI培训内容,2天)

人民币4980元/人(包含AI培训内容,3天)

交通、食宿等费用请自理。

4.优惠活动:

两人报名参加,享9.5折优惠;

三人及以上报名参加,享9.0折优惠;

本次多人报名优惠活动,最终解释权归依元素科技所有。

5.缴费方式:支持提前转账和现场缴费。

九、指定收款账户

户 名:深圳市依元素科技有限公司北京分公司

开户行:招商银行股份有限公司北京中关村支行

帐 号:110911478810902

十、报名方式

报名链接:http://www.e-elements.com/baoming/bm/id/35.shtml

二维码报名:(报名截止时间为2020年8月27日)

十一、联系方式

依元素科技有限公司

联系人:张剑森 18165756976 kenson.zhang@e-elements.com

赵冬雪 15044301196 nancy.zhao@e-elements.com

传 真:0755-86186700

座 机:0755-86186715

附件:

日程安排

| 8月29日 – MPSoC软硬件开发 | |

| 时间 | 课程主题 |

| 9:00 - 9:30 | 报到注册 |

| 9:30 – 10:15 | Zynq UltraScale+ MPSoC 简介 |

| 10:15 – 11:00 | APU组成 |

| 11:00 – 11:15 | 休息 |

| 11:15 – 12:00 | 实验1:搭建一个Zynq UltraScale+ MPSoC系统,配置PS并添加PL外设 |

| 12:00 – 13:15 | 午餐 |

| 13:15 – 14:30 | RPU组成 硬件/软件虚拟化 |

| 14:30 – 15:00 | 安全和软件测试 |

| 15:00 – 15:15 | 休息 |

| 15:15 – 16:15 | 功耗管理 系统一致性 |

| 16:15 – 17:00 | DDR和QoS 实验2:如何配置DDR以获得系统最佳性能 |

| 17:00 – 17:15 | 课后交流 |

| 8月30日 – MPSoC软硬件开发 | |

| 时间 | 课程主题 |

| 9:30 – 10:00 | 时钟和复位 |

| 10:00 – 11:00 | AXI PS/PL互联 |

| 11:00 – 11:15 | 休息 |

| 11:15 – 12:00 | 实验3:调用AXI Traffic Generator IP,实现 AXI数据传输 |

| 12:00 – 13:15 | 午餐 |

| 13:15 – 14:15 | 实验4:通过HP端口访问DDR实现数据交互 实验5:通过HPC端口访问DDR,保证缓存一致性 |

| 14:15 – 15:15 | 启动和配置 |

| 15:15 – 15:30 | 休息 |

| 15:30 – 16:30 | 实验6:如何生成启动镜像文件并上电加载 |

| 16:30 – 17:00 | 系统调试 |

| 17:00 – 17:15 | 课后交流 |

| 8月31日 – Vitis AI开发 | |

| 时间 | 课程主题 |

| 9:30 – 10:15 | 介绍Vitis AI开发环境 |

| 10:15 – 11:00 | 机器学习基本概念 基于Vitis AI 的DPU开发与环境配置 |

| 11:00 – 11:15 | 休息 |

| 11:15 – 12:00 | 实验1:Vitis AI 的DPU开发与环境配置 |

| 12:00 – 13:15 | 午餐 |

| 13:15 – 14:00 | DPU介绍 |

| 14:00 – 15:15 | DPU-V1架构介绍 DPU-V2架构介绍 |

| 15:15 – 15:30 | 休息 |

| 15:30 – 16:15 | Vitis AI库 |

| 16:15 – 17:00 | 实验2:基于图片和视频的应用开发 实验3:基于摄像头的人脸实时检测应用 |

| 17:00 – 17:15 | 课后交流 |

最新活動

- Thursday 22, 2025

- Monday 12, 2025

- Monday 21, 2025

- Friday 18, 2025

- Thursday 03, 2025

- Friday 07, 2025

- Thursday 13, 2025

- Monday 13, 2025

- Monday 30, 2024

- Friday 29, 2024

- Wednesday 20, 2024

- Monday 18, 2024

- Wednesday 06, 2024

- Tuesday 29, 2024

- Friday 18, 2024

- Tuesday 14, 2020

公司新闻

- Thursday 22, 2025

- Monday 12, 2025

- Monday 21, 2025

- Friday 18, 2025

- Thursday 03, 2025

- Friday 07, 2025

- Thursday 13, 2025

- Monday 13, 2025

- Monday 30, 2024

- Wednesday 20, 2024

- Monday 18, 2024

- Wednesday 06, 2024

- Tuesday 29, 2024

- Friday 18, 2024

- Tuesday 14, 2020