依元素科技高级FPGA培训课程系列—基于AMD FPGA的高级时序约束和设计收敛技术

AMD采用先进的EDA技术和方法,结合其合作伙伴生态系统为软硬件开发环境和嵌入式平台提供一整套功能强大的工具、设计库和设计方法。这些环境不仅可缩短开发时间,同时还可帮助开发者按需轻松创建定制硬件加速器。本课程主要围绕全新的Vivado设计工具套件,提供全新构建的自适应SoC增强型、以IP和系统为中心的开发环境,便于解决系统级集成和实现的生产力瓶颈,可显著提高设计生产力和设计结果质量,使设计者更好、更快地创建系统, 而且所用的芯片资源更少。此课程重心聚焦在设计开发者们最常见的时序约束和静态时序分析、时序收敛、UltraFast设计优化方法、功耗优化等。

一、 培训对象

1. FPGA硬件设计开发者,可提供技能提升储备;

2. FPGA底层软件开发者跨向硬件设计领域,可提供软硬件系统设计参考;

3. 本课程特别适合FPGA工程师在最新UltraScale/UltraScale+或7 系列产品开发上作为提高设计生产力并加速新产品面世的进程。

二、 培训目标

1. 学会如何进行时序约束和静态时序分析;

2. 学会如何针对系统同步和源同步接口设置适合的时序约束;

3. 学会分析时序异常并采取适合的解决手段;

4. 学会多种时序收敛手段,减少延迟;

5. 学会如何最优化HDL编码技术、复位技术、流水线技术、同步设计技术等;

6. 学会基本的功耗优化收敛技术。

三、 学员基础

1. 具有一定的HDL语言基础

2. 基本了解FPGA架构

3. 具有一定的Vivado工具使用经验为佳

四、 教学平台

现场提供AMD官方开发板用于动手实验

五、 软件工具

Vivado ML Edition 2022.2或以上版本

六、 师资团队

讲师团队来自于全球领先的可编程逻辑解决方案提供商AMD(即Xilinx)公司的授权培训讲师及行业精英组成,具备顶尖FPGA系统设计技术,并有丰富的FPGA系统项目经验。领先的FPGA理论和丰富的实战经验,将带给学员以从不同的视角来审视和掌握FPGA系统开发的精髓。

部分师资介绍:

Robert Zhou:知名高校硕士学位,具有10年以上FPGA项目开发和技术支持经验,并具有多年的FPGA企业培训经验。

Kenson Zhang:AMD官方认证培训讲师,具有多年的FPGA技术支持和教学培训经验,AMD公司亚太区最佳讲师之一。

七、 培训收益

本课程将为基于最新版本的Vivado® Design Suite,了解相关数据库和静态时序分析 (STA) 机制,创建 AMD 设计约束 (XDC) 并学会静态时序分析;学习如何为您的 FPGA 设计的 SDR、DDR、源同步和系统同步接口制定适当的时序约束;学习如何利用系统复位技术、同步电路技术、最优化HDL编码技术和时序收敛技术及功耗收敛技术来提高设计性能和稳定性。

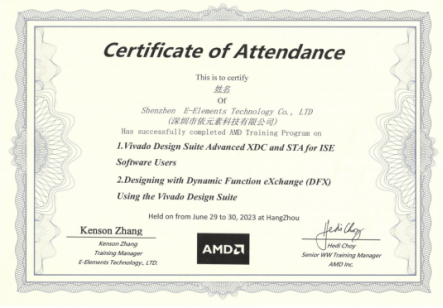

八、 证 书

培训结束,理论、实践双项考核成绩合格者, 颁发AMD官方授权培训FPGA工程师证书。

颁发AMD官方授权培训FPGA工程师证书。

九、 培训时间和地点

时间: 2023年10月28日-29日,每天9:30am-17:15pm

地点: 南京市江北新区集成电路产业服务中心依元素科技南京培训基地(地铁三号线星火路站附近)

十、 培训费用

费用:人民币3300元/人(含教材、实验资料、午餐和学习用具等),食宿费用请自理。

特惠:10月22日前完成报名和缴费,享96折优惠; 三人及以上报名,享92折优惠。

(本活动最终解释权归依元素科技所有)

十一、 指定收款账户

户 名:深圳市依元素科技有限公司北京分公司

开户行:招商银行股份有限公司北京中关村支行

帐 号:110911478810902

十二、 报名与课程咨询联系方式

报名链接: http://www.e-elements.com/baoming/bm/id/100.shtml

课程内容咨询: 张剑森 18165756976 kenson.zhang@e-elements.com

课程报名咨询: 胡海燕 13814168632 haiyan.hu@e-elements.com

基于AMD FPGA的高级时序约束和设计收敛技术课程大纲

Day 1 | |

时间 | 课程主题 |

9:30–10:30 | Ø 时钟约束简介 Ø 生成时钟 Ø 时钟网络报告 |

10:30–10:40 | 休息 |

10:40–12:00 | Ø 时钟分组约束 Ø I/O约束和虚拟时钟 Ø 时序约束向导 Ø 实验1:IO约束和虚拟时钟 |

12:00–13:20 | 午餐 |

13:20–14:30 | Ø Vivado报告简介 Ø Setup和Hold时序分析 Ø 时序概要报告 Ø 时钟互联报告 |

14:30–14:40 | 休息 |

14:40–15:40 | Ø 时序例外约束 Ø 时序优先级 Ø 实验2:时序例外 |

15:40–15:50 | 休息 |

15:50–17:00 | Ø 同步电路设计 Ø Datasheet报告 Ø 时序基线技术 Ø 实验3:时序基线 |

17:00–17:15 | 课后答疑 |

Day 2 | |

时间 | 课程主题 |

9:30–10:30 | Ø HDL编码技术 Ø 流水线技术 Ø 复位技术 |

10:30–10:40 | 休息 |

10:40–12:00 | Ø I/O时序简介 Ø 系统同步I/O时序 Ø 源同步I/O时序 Ø 实验4:源同步I/O时序 |

12:00–13:20 |

午餐 |

13:20–14:30 | Ø Floorplan区域约束 Ø 物理最优化 Ø UltraFast设计方法学-时序收敛 |

14:30–15:40 | 休息 |

15:40–17:00 | Ø 减少逻辑延迟 Ø 减少布线延迟 Ø 改善时钟skew Ø 改善时钟抖动 Ø 功耗优化收敛技术 Ø 实验5: 时序收敛和设计优化 |

17:00–17:15 | 课后答疑 |

最新活動

- Thursday 22, 2025

- Monday 12, 2025

- Monday 21, 2025

- Friday 18, 2025

- Thursday 03, 2025

- Friday 07, 2025

- Thursday 13, 2025

- Monday 13, 2025

- Monday 30, 2024

- Friday 29, 2024

- Wednesday 20, 2024

- Monday 18, 2024

- Wednesday 06, 2024

- Tuesday 29, 2024

- Friday 18, 2024

- Tuesday 14, 2020

公司新闻

- Thursday 22, 2025

- Monday 12, 2025

- Monday 21, 2025

- Friday 18, 2025

- Thursday 03, 2025

- Friday 07, 2025

- Thursday 13, 2025

- Monday 13, 2025

- Monday 30, 2024

- Wednesday 20, 2024

- Monday 18, 2024

- Wednesday 06, 2024

- Tuesday 29, 2024

- Friday 18, 2024

- Tuesday 14, 2020