依元素科技高级FPGA培训课程系列—基于AMD FPGA的高速接口设计和实现

随着装备数字化技术和微电子技术的发展,可编程逻辑嵌入式系统设计技术应用已遍及航空航天、医疗、通讯、网络通讯、安防、广播、汽车电子、工业、消费类市场、测量测试等多个热门领域。现代大型装备系统对于效能与信息安全要求越来越高,越来越多的设计也开始由ASIC转向FPGA,可编程逻辑已成为目前项目开发人员不可或缺的开发技术。并且,许多基于FPGA的应用领域都对数据传输速率和带宽的要求越来越高,早已经达到千兆/万兆位级的传输速率,并还在继续加快的趋势。

依元素科技特举办为期2天的高速接口专题培训班,帮助有一定FPGA开发经验的设计者掌握如何使用AMD FPGA的高速串行收发器来实现高速率高带宽的数据传输,并介绍常见的应用传输协议如Aurora、以太网、PCIe、JESD204、Interlaken等;并进一步通过实际案例来介绍如何调用IP核实现DDR3/DDR4接口设计、千兆以太网和10G光口设计等,达到具备AMD FPGA高速接口设计和调试的基本能力。

一、 培训特色:

1. 培训为期2天,结合案例分析,全面细致地讲解基于AMD FPGA高速接口设计的相关理论及其设计实现。

2. 本课程使用最新版本AMD全球统一的授权培训课件,可以满足实际工程设计的需求。

3. 本课程由AMD官方授权认证专家授课,授课教师具有多年的项目开发经验。

4. 培训采用AMD官方硬件平台,可动手实战操作。

5. 课程配套有丰富的实验案例,由浅入深,理论与实践相结合,注重提高学员的动手能力。

6. 为学员配置齐全的实验指导手册,学员可参考手册,在教师辅导下完成全部实验。

二、 培训目标:

1.了解AMD高速串行收发器模块的结构和特性;

2.学会利用收发器结构向导IP来生成MGT接口工程;

3.学会MGT设计执行、仿真和实现,并做测试和调试;

4.了解高速串行收发器应用的常见传输协议:Aurora、PCIe、JESD204、Interlaken、以太网;

5.学会如何使用MIG IP核实现DDR4接口设计;

6.学会如何使用以太网IP核实现千兆以太网接口设计。

三、 培训对象:

课程适合具有一定FPGA开发经验的研发工程师或技术支持工程师,特别适合在无线通讯、有线通讯、视频和图像处理、高性能计算等领域进行高吞吐量数据传输和处理的应用开发人员。

四、 学员基础:

1.具备Verilog或VHDL开发经验

2.了解FPGA架构和AMD开发工具

3.具有一定的FPGA设计经验或学习过FPGA设计基础课程

4.了解高速串行I/O协议和标准更佳

五、 教学平台:

AMD Zynq UltraScale+ MPSoC系列平台ZCU104

六、 软件工具:

Vivado ML Edition 2020.1或以上版本

七、 师资团队:

讲师团队由AMD公司的授权培训讲师及行业精英组成,具备顶尖的FPGA系统设计技术,并有丰富的FPGA系统项目经验。部分师资介绍:

Robert Zhou:熟悉各种AMD FPGA高速接口,具有10年以上FPGA项目开发和技术支持经验,并具有多年的FPGA企业培训经验。

Kenson Zhang:AMD官方认证培训讲师,具有多年的FPGA技术支持和教学培训经验,AMD公司亚太区最佳讲师之一。

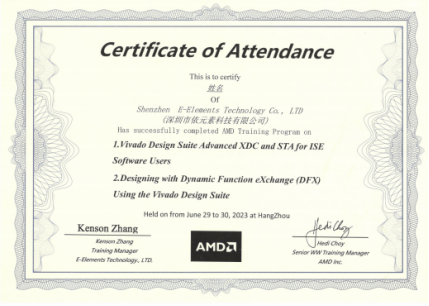

八、 证 书:

培训结束,理论、实践双项考核成绩合格者,颁发AMD官方授权培训FPGA工程师证书。

九、时间和地点

时间:2023年12月23日-12月24日,每天9:15am-17:15pm

地点:南京江北新区依元素科技南京培训基地

十、 培训缴费

课程费用:人民币3500元/人(含资料、午餐、学习用具等),交通、住宿等费用自理。

优惠活动:

u两人报名参加,享9.6折优惠;

u三人及以上报名参加,享9.2折优惠;

(本次报名优惠活动,最终解释权归依元素科技所有)。

缴费方式:支持提前转账和现场缴费。

十一、 指定收款账户

户 名:深圳市依元素科技有限公司北京分公司

开户行:招商银行股份有限公司北京中关村支行

帐 号:110911478810902

十二、 报名方式:

报名链接:http://www.e-elements.com/baoming/bm/id/102.shtml

二维码报名:(报名截止时间为2023年12月22日)

十三、 联系方式

依元素科技有限公司

课程内容联系人: 张经理 18165756976 kenson.zhang@e-elements.com

课程报名联系人:胡小姐 13814168632 haiyan.hu@e-elements.com

座 机:025-58800523 & 010-82757632

传 真:0755-86186700

培训日程安排

Day1 | |

时 间 | 课程主题 |

9:15 – 10:15 | Ø 收发器概述 |

10:15 –10:45 | Ø 收发器时钟和复位 |

10:45 – 11:00 | 休 息 |

11:00 – 12:00 | Ø 收发器向导简介 Ø 实验 1:生成收发器内核 – 利用收发器向导创建实例化模板。 |

12:00 – 13:15 | 午 餐 |

13:15 – 14:15 | Ø 收发器仿真 Ø 实验 2:仿真 – 使用 IP 范例设计仿真收发器 IP。 |

14:15 – 15:15 | Ø PCS层介绍 Ø 实验 3: 64B/66B编码 |

15:15 – 15:30 | 休 息 |

15:30 – 16:30 | Ø 收发器实现 Ø 实验 4:实现 – 使用 IP 范例设计实现收发器 IP。 |

16:30 – 17:00 | Ø PMA层介绍 |

17:00 – 17:15 | 课后答疑 |

Day2 | |

时间 |

课程主题 |

9:15 – 9:45 | Ø PMA层优化 |

9:45 – 10:45 | Ø 实验 5: IBERT设计 – 创建 IBERT 设计,验证物理链路 |

10:45 – 11:00 | 休息 |

11:00 – 12:00 | Ø 收发器测试和调试。 Ø 实验 6: 收发器调试 – 使用 IP 范例设计和 Vivado 调试核调试收发器 IP。 |

12:00 – 13:15 |

午餐 |

13:15 – 13:45 | Ø 收发器板级设计要求 |

13:45 – 14:45 | Ø 收发器应用案例:Aurora、Networking、Interlaken、PCIe、JESD204 |

14:45 – 15:00 | Ø 休息 |

15:00 – 16:00 | Ø MIG IP核实现DDR4接口设计 |

16:00 – 17:00 | Ø 使用以太网IP实现千兆网口设计 |

17:00 –17:15 | 课后答疑 |

最新活動

- Thursday 22, 2025

- Monday 12, 2025

- Monday 21, 2025

- Friday 18, 2025

- Thursday 03, 2025

- Friday 07, 2025

- Thursday 13, 2025

- Monday 13, 2025

- Monday 30, 2024

- Friday 29, 2024

- Wednesday 20, 2024

- Monday 18, 2024

- Wednesday 06, 2024

- Tuesday 29, 2024

- Friday 18, 2024

- Tuesday 14, 2020

公司新闻

- Thursday 22, 2025

- Monday 12, 2025

- Monday 21, 2025

- Friday 18, 2025

- Thursday 03, 2025

- Friday 07, 2025

- Thursday 13, 2025

- Monday 13, 2025

- Monday 30, 2024

- Wednesday 20, 2024

- Monday 18, 2024

- Wednesday 06, 2024

- Tuesday 29, 2024

- Friday 18, 2024

- Tuesday 14, 2020