EXOSTIV

高速FPGA设计调试方案:EXOSTIV Probe

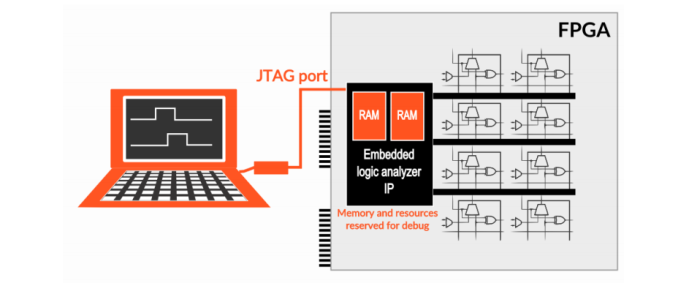

相信每一个电子工程师在项目开发的过程中都不可避免的要进行方案的调试,除了模拟调试我们还必须进行真机调试才能确保功能的正常,通常我们采用的调试方法分为两种:第一种是使用硬件逻辑分析仪,第二种是采用嵌入逻辑分析IP,通过JTAG连接开发IDE进行调试,但是随着FPGA设计越来越复杂,速度越来越快,这两种方案显得越来越捉襟见肘,逻辑分析仪会占用太多的FPGA I/O接口,嵌入式逻辑分析IP又会消耗宝贵的FPGA逻辑资源,因此Exostiv Labs公司推出了新型的调试工具EXOSTIV Probe。

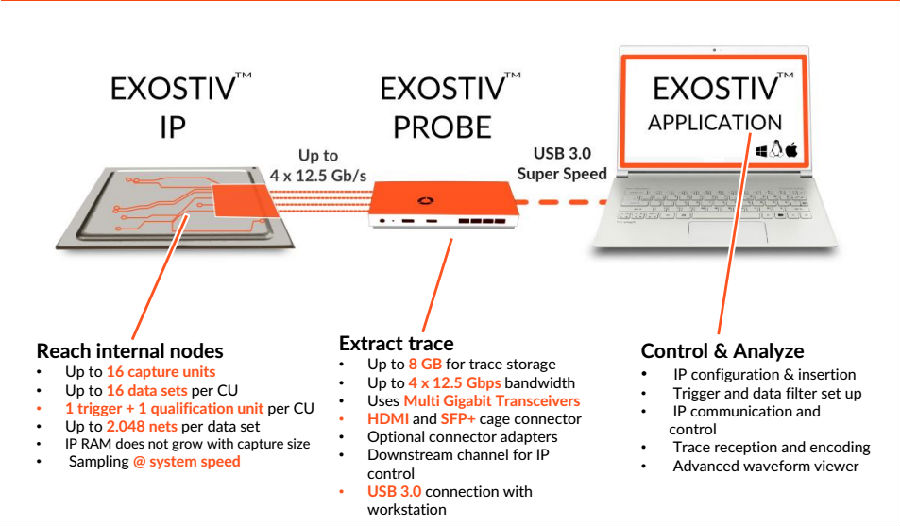

EXOSTIV Probe从各方面都优于传统方案,它支持Xilinx All Programmable所有系列,采用高速SerDes接口实现数据采集和通信,EXOSTIV Probe能够采集多达32768个内部信号节点,此外EXOSTIV IP提供动态多路复用控制功能,能够动态采集更多的数据集而不需要重新进行编译。

调试手段 (一)传统 Logic Analyzer’调试方式

调试手段(二)Embedded Logic Analyzer’approach

EXOSTIV Probe提供8GB的存储空间用于存储从FPGA中采集到的数据,高速USB 3.0接口用于实现EXOSTIV应用上位机与EXOSTIV之间的通信,集成了四个SFP/SFP+收发器接口,每个接口速度可达6.6Gbps。此外上位机EXOSTIV Dashboard由Core Inserter和Analyzer两大功能组件组成,Core Inserter可以动态配置EXOSTIV IP,Analyzer则实现采集数据的管理、显示分析并且导出,MYRIAD波形显示插件支持TB级波形数据的显示。

产品简介 :

EXOSTIVTM探针采用FPGA的串行收发器将捕获到的数据流放到一个外部存储器,并为调试数据提供了多达8GB的存储空间。

EXOSTIVTM仪表板软件包括MYRIAD,是该行业的第一款能够处理兆字节数字和模拟波形数据的波形阅读器。

EXOSTIVTM的IP支持重复捕获多达32,768个内部节点并同时具有fpga的运算速度。EXOSTIVTM IP提供动态多路复用器控制以捕获更多的数据集,同事减少了重新编译FPGA的需要。

数据集的动态开/关控制保留收发器带宽用于更深层次的捕获。

特性:

-支持芯片系列: Zynq,Series7&Ultrascale(+)

-要求用Vivado综合和插入IP

-EXOSTIV™ 探针有8GB的外部存储

-高达4 x 12.5 Gbps 的收发器连接

。SFP/SFP+/QSFP/QSFP + cages

。用户接口(HDMI 或 mini/micro-HDMI)

。FMC和其他 (如适配器)

-MYRIADTM波形查看器(TB-capable)

-USB 3.0 接口与电脑连接

-可配置的嵌入式仪器IP

-RTL或综合后进行IP的插入

-复杂的数据复用

-过渡存储

-数据分类/数据过滤

-TCL/tk 脚本接口

最新活動

- Thursday 22, 2025

- Monday 12, 2025

- Monday 21, 2025

- Friday 18, 2025

- Thursday 03, 2025

- Friday 07, 2025

- Thursday 13, 2025

- Monday 13, 2025

- Monday 30, 2024

- Friday 29, 2024

- Wednesday 20, 2024

- Monday 18, 2024

- Wednesday 06, 2024

- Tuesday 29, 2024

- Friday 18, 2024

- Tuesday 14, 2020

公司新闻

- Thursday 22, 2025

- Monday 12, 2025

- Monday 21, 2025

- Friday 18, 2025

- Thursday 03, 2025

- Friday 07, 2025

- Thursday 13, 2025

- Monday 13, 2025

- Monday 30, 2024

- Wednesday 20, 2024

- Monday 18, 2024

- Wednesday 06, 2024

- Tuesday 29, 2024

- Friday 18, 2024

- Tuesday 14, 2020