-

产品介绍

产品介绍

特色

特色 产品规格

产品规格 实物图片

实物图片 资源

资源

系统原型验证平台

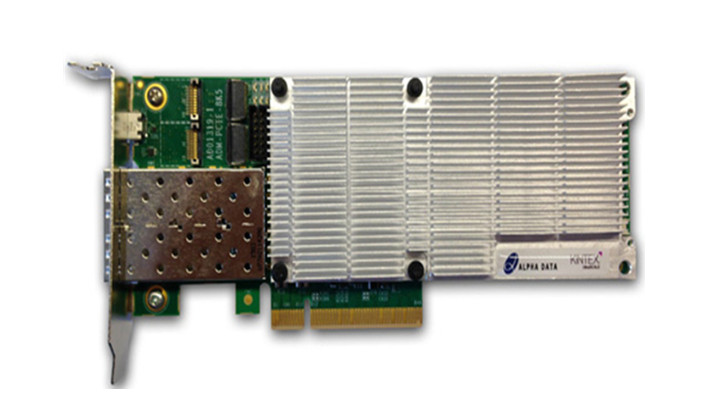

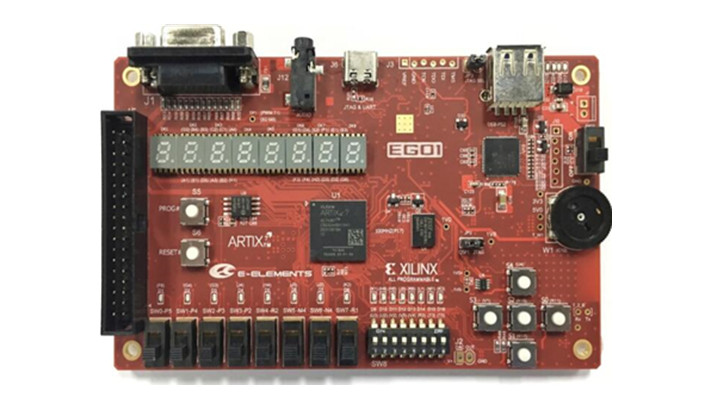

随着芯片集成度提高和性能的多元化, 大规模集成电路设计复杂性的提升,使芯片验证面临巨大挑战。基于Xilinx可编程逻辑门阵列(FPGA)建立有效的原型验证平台已成为芯片开发设计验证的主要选择。 而原型验证需要使用的子板种类多样,很多时候需要客制化设计,进一步给调试带来了不确定性,也延长了调试周期。依元素科技提供基于新思科技HAPS原型验证解决方案, 给用户提供了多种灵活的接口方案,包含丰富的外部子卡集合,降速与同步方案, 并通过HAPS Connect Program,为使用者提供了更广泛的扩展空间。

![]() HAPS Customization Daughter Boards and IP Validation

HAPS Customization Daughter Boards and IP Validation

Customized and integrated Synopsys MIPI IP with SMF board to work with HAPS prototyping system

Customized HT3 daughter board design with Intel IP to validate on HAPS prototyping system

Validated PCIeGen5 32G on HAPS prototyping system

Evaluation board with DM.2 on HAPS Zebu system

系统层级自动化设计工具

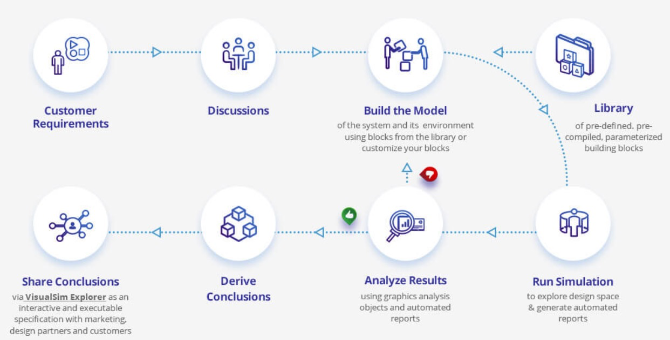

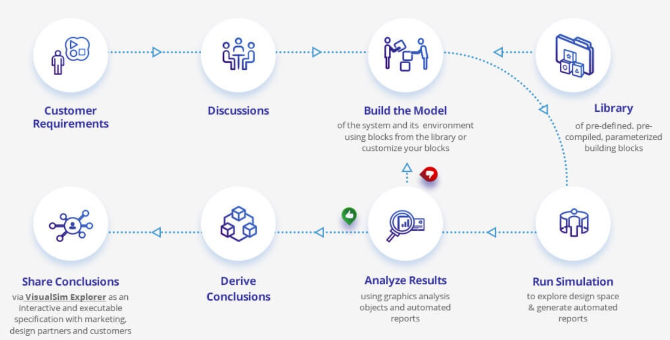

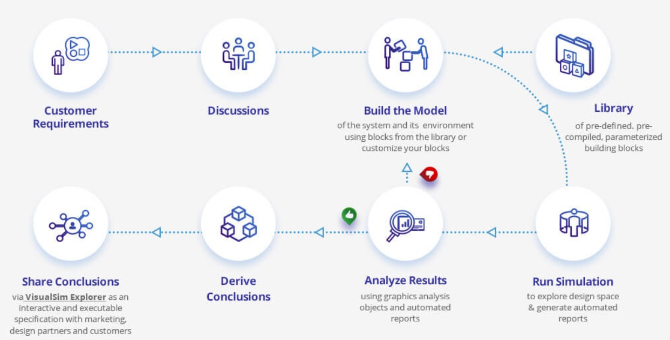

系统及单晶片架构探索以及设计验证平台,不仅免去了构建模型的工程,同时也加速了复杂设计的模拟。这种作法让团队不用花费大量的时间和精力在建立复杂设计的模型上,对于基于模型设计方法的设计项目而言,这不仅确保了模型的正确性,也大幅缩短了产品开发时长。 系统层级自动化设计工具包含:软件自动化设计模拟软件、丰富模型库。

![]() Hardware Design

Hardware Design

Functional correctness, speed, topology and arbitration

![]() Software Development

Software Development

Quality, traffic stimulus, impact of configuration and power

![]() Performance Analysis

Performance Analysis

Throughput, response time, Buffer size and utilization

![]() Power Measurement

Power Measurement

Peak and average power, energy and power/task

![]() Functional safety Analysis

Functional safety Analysis

ISO-26262 and RO-254 certifications

系统原型验证平台

随着芯片集成度提高和性能的多元化, 大规模集成电路设计复杂性的提升,使芯片验证面临巨大挑战。基于Xilinx可编程逻辑门阵列(FPGA)建立有效的原型验证平台已成为芯片开发设计验证的主要选择。 而原型验证需要使用的子板种类多样,很多时候需要客制化设计,进一步给调试带来了不确定性,也延长了调试周期。一元素科技提供基于新思科技HAPS原型验证解决方案, 给用户提供了多种灵活的接口方案,包含丰富的外部子卡集合,降速与同步方案, 并通过HAPS Connect Program,为使用者提供了更广泛的扩展空间。

![]() HAPS Customization Daughter Boards and IP Validation

HAPS Customization Daughter Boards and IP Validation

Customized and integrated Synopsys MIPI IP with SMF board to work with HAPS prototyping system

Customized HT3 daughter board design with Intel IP to validate on HAPS prototyping system

Validated PCIeGen5 32G on HAPS prototyping system

Evaluation board with DM.2 on HAPS Zebu system

系统层级自动化设计工具

系统及单晶片架构探索以及设计验证平台,不仅免去了构建模型的工程,同时也加速了复杂设计的模拟。这种作法让团队不用花费大量的时间和精力在建立复杂设计的模型上,对于基于模型设计方法的设计项目而言,这不仅确保了模型的正确性,也大幅缩短了产品开发时长。 系统层级自动化设计工具包含:软件自动化设计模拟软件、丰富模型库。

![]() Hardware Design

Hardware Design

Functional correctness, speed, topology and arbitration

![]() Software Development

Software Development

Quality, traffic stimulus, impact of configuration and power

![]() Performance Analysis

Performance Analysis

Throughput, response time, Buffer size and utilization

![]() Power Measurement

Power Measurement

Peak and average power, energy and power/task

![]() Functional safety Analysis

Functional safety Analysis

ISO-26262 and RO-254 certifications

系统原型验证平台

随着芯片集成度提高和性能的多元化, 大规模集成电路设计复杂性的提升,使芯片验证面临巨大挑战。基于Xilinx可编程逻辑门阵列(FPGA)建立有效的原型验证平台已成为芯片开发设计验证的主要选择。 而原型验证需要使用的子板种类多样,很多时候需要客制化设计,进一步给调试带来了不确定性,也延长了调试周期。一元素科技提供基于新思科技HAPS原型验证解决方案, 给用户提供了多种灵活的接口方案,包含丰富的外部子卡集合,降速与同步方案, 并通过HAPS Connect Program,为使用者提供了更广泛的扩展空间。

![]() HAPS Customization Daughter Boards and IP Validation

HAPS Customization Daughter Boards and IP Validation

Customized and integrated Synopsys MIPI IP with SMF board to work with HAPS prototyping system

Customized HT3 daughter board design with Intel IP to validate on HAPS prototyping system

Validated PCIeGen5 32G on HAPS prototyping system

Evaluation board with DM.2 on HAPS Zebu system

系统层级自动化设计工具

系统及单晶片架构探索以及设计验证平台,不仅免去了构建模型的工程,同时也加速了复杂设计的模拟。这种作法让团队不用花费大量的时间和精力在建立复杂设计的模型上,对于基于模型设计方法的设计项目而言,这不仅确保了模型的正确性,也大幅缩短了产品开发时长。 系统层级自动化设计工具包含:软件自动化设计模拟软件、丰富模型库。

![]() Hardware Design

Hardware Design

Functional correctness, speed, topology and arbitration

![]() Software Development

Software Development

Quality, traffic stimulus, impact of configuration and power

![]() Performance Analysis

Performance Analysis

Throughput, response time, Buffer size and utilization

![]() Power Measurement

Power Measurement

Peak and average power, energy and power/task

![]() Functional safety Analysis

Functional safety Analysis

ISO-26262 and RO-254 certifications