-

产品介绍

产品介绍

特色

特色 产品规格

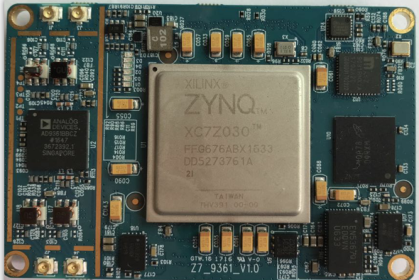

产品规格 实物图片

实物图片 资源

资源

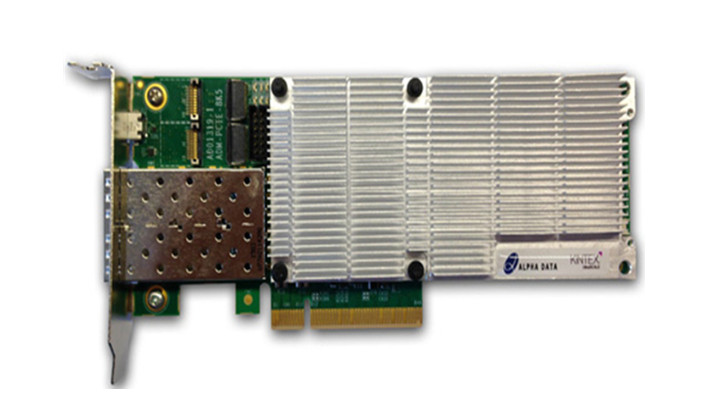

该开发板含有信息与通信处理单元(包含互联网路由器、无线通信网络控制器、通信传输与信号处理电路)和宽带射频收发信机,支持通信工程学科的综合实验。

收发信机主要完成数字/模拟转换、正交解制/解调、信号放大与增益自动控制、接收低噪放大与发送可编程功率输出。

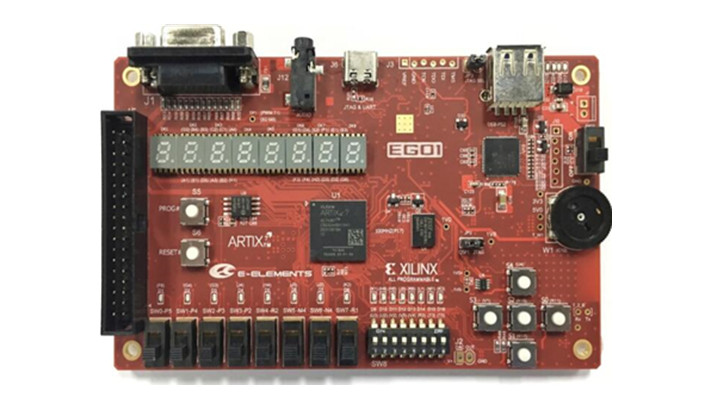

该开发板主要用于无线通信的实验教学,还可以用来开设嵌入式技术、移动互联技术、物联网技术等相关课程。实验项目以二次开发和创新性实验为主,学生还可以开展课外创新实践。

采用核心板加底板架构模式,提供了稳定的CPU最小系统模块,方便二次开发,可应用在不同的创新实验或实践中。

(1)信息与通信处理单元

采用Xilinx Zynq-7000 All Programmable SoC平台,ARM处理器和FPGA架构紧密集成,拥有双核ARM Cortex-A9MPCore的高性能,低功耗特性,同时采用低功耗DDR2,便携长时间外场开发测试。

(2)宽带射频收发信机

收发信机采用ADI公司的AD9361射频收发器实现宽带无线信号的双发双收功能,频率覆盖70MHZ~6GHZ。

u 通信核心板平台配置如下表所示:

通信核心板硬件配置 | |

射频单元 | Analog Devices AD9361 integrated RF Agile Transceiver,与处理单元采用LVDS接口 |

频率范围 | 70MHz ~ 6.0GHz |

信号带宽 | 200kHz ~ 56MHz |

射频通道 | 2TX,2RX |

发射功率 | P1B≥12dBm |

基带处理单元 | Xilinux Zynq XC7Z030 FFG676 AP SoC |

CPU | Dual ARM Cortex -A9 MPCore at 800MHz |

逻辑单元 | Kintex-7 logic cells with DSP 48E1 slices |

存储器DDR | 256MB(2Gb) LPDDR2 |

存储器FLASH | 256Mb QSPI Flash |

网口PHY | 10M/100M/1000M速率自适应, |

USB PHY | 支持USB2.0 OTG2.0 |

电源供电 | 支持3.3V 供电 |

通信底板硬件配置 | |

网口 | 支持10M/100M/1000M速率自适应以太网RJ45连接器 |

USB口 | 支持micro USB Host/Slave 2.0接口 |

SDIO口 | 支持MMC3.31, Push-Push T卡 |

UART口 | 支持3线TTL UART口,支持232电平转换UART口 |

I2C口 | 支持I2C V2标准协议 |

SPI口 | 支持3线/4线主从模式 |

ADC口 | 支持2路差分 |

射频接口 | 4个IPEX和4个SMA接口,带有RF PA 和RF LNA,支持双发双收功能 |

音频接口 | 具有音频CODEC,在8K~96K的频率内提供16bit、20bit、24bit和32bit的采样;支持MIC、Headphone,Line-in功能 |

Jtag口 | 支持Xilinx Jtag仿真器 |

电源 | 物理接口为5V DC插座,电源输入为5V直流电源。 |